Тиждень ФКІТ

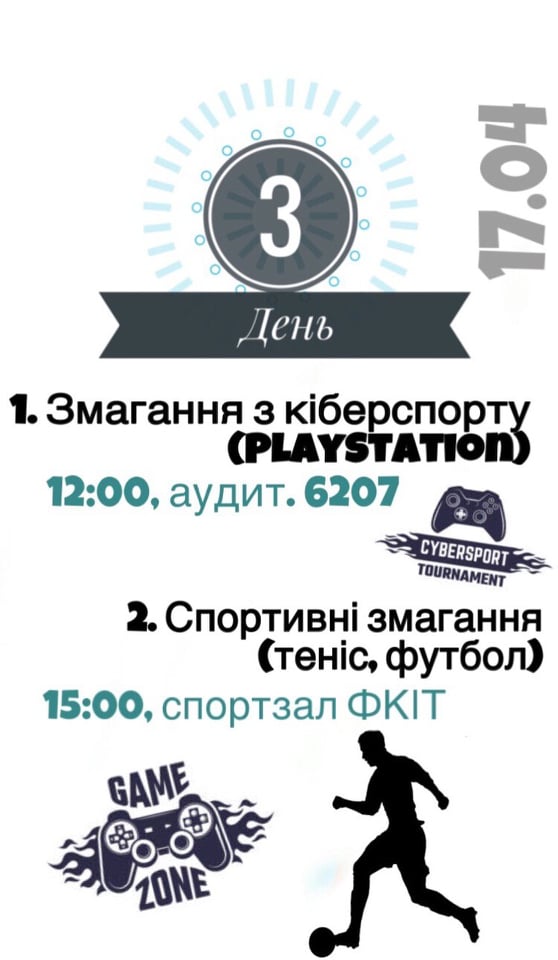

15 – 19 квітня 2019 року буде проходити тиждень ФКІТ, передбачені такі заходи:

- інтелектуальна гра «Що? Де? Коли?»

- конкурс на найкращу кімнату в гуртожитку;

- спортивні змагання;

- змагання з кіберспорту.

Те ще багато цікавого!

15 – 19 квітня 2019 року буде проходити тиждень ФКІТ, передбачені такі заходи:

Те ще багато цікавого!

Посада: викладач

Е-mail: a7davletova@gmail.com

Освіта

• В 2004 році закінчила Тернопільську академію народного господарства за спеціальністю «Банківська справа» та отримала кваліфікацію магістра з банківської справи.

• В 2016 закінчила Тернопільський національний економічний університет за спеціальністю «Програмне забезпечення систем» та отримала кваліфікацію магістра.

Посада: інженер кафедри СКС

Освіта

• В 2003 році закінчила Тернопільську академію народного господарства за спеціальністю «Фінанси» та отримала кваліфікацію економіста.

Патент на корисну модель

КРУЛІКОВСЬКИЙ БОРИС БОРИСОВИЧ; ВОЗНА НАТАЛІЯ ЯРОСЛАВІВНА; ГРИГА ВОЛОДИМИР МИХАЙЛОВИЧ; НИКОЛАЙЧУК ЯРОСЛАВ МИКОЛАЙОВИЧ; ДАВЛЕТОВА АЛІНА ЯРОСЛАВІВНА

Суматор з прискореним переносом належить до засобів обчислювальної техніки та швидкодіючих компонентів арифметико-логічних пристроїв процесорів цифрового опрацювання сигналів та даних. Пристрій містить 2n-розрядну вхідну шину, (k=n/m), m -розрядних суматорів, на перші входи переносу яких поданий логічний “0”, (k-1) m-розрядних суматорів на перші входи переносу яких подана логічна “1”, (k-1) m+1-розрядних двовходових мультиплексорів з першими прямими керуючими входами, n+1-розрядну вихідну шину, в якому додатково введені інкрементні суматори з входом переносу логічної одиниці, входи яких додатково з’єднані з інформаційними виходами m-розрядних суматорів з входами переносу логічного нуля та додатково введений інверсний вихід у першому m-розрядному суматорі з входом переносу логічного нуля та додатково введені інверсні входи та виходи у кожному парафазному мультиплексорі. Технічним результатом є зменшення апаратної складності в 2 рази та підвищення швидкодії у 1,5 рази.

Патент на корисну модель

НИКОЛАЙЧУК ЯРОСЛАВ МИКОЛАЙОВИЧ; ГРИГА ВОЛОДИМИР МИХАЙЛОВИЧ; ВОЗНА НАТАЛІЯ ЯРОСЛАВІВНА; ДАВЛЕТОВА АЛІНА ЯРОСЛАВІВНА

Повний однорозрядний суматор належить до засобів обчислювальної техніки і може бути використаний як компонент багаторозрядних двійкових суматорів арифметико-логічних пристроїв мікропроцесорів та спецпроцесорів сортування даних. Пристрій містить два інформаційні входи, вихід суми та інверсні вхід та вихід переносів. Додатково суматор містить три логічні елементи «Виключаюче АБО», які реалізовані на двох монтажно з’єднаних виходами логічних елементів І-НЕ та АБО. Додатково суматор містить перший логічний елемент НЕ, який з’єднаний з першим вдом третього логічного елемента «Виключаюче АБО» та другий логічний елемент НЕ, який з’єднаний з другим входом другого логічного елемента «Виключаюче АБО». Технічним результатом є підвищення у 2 рази швидкодії формування сигналів переносу

Патент на корисну модель

СИДОР АНДРІЙ ІВАНОВИЧ; НИКОЛАЙЧУК ЯРОСЛАВ МИКОЛАЙОВИЧ; ВОЗНА НАТАЛІЯ ЯРОСЛАВІВНА

Різницево-модульний квадратор, який містить першу вхідну шину, логічні модулі рандомізаціїта вихідну шину, яка з’єднана з виходами логічних модулів рандомізації, який відрізняється тим, що згідно з винаходом перша вхідна шина додатково з’єднана з першими входами першого та другого додатково введених модульних регістрів пам’яті, додатково введена друга вхідна шина з’єднана з другим входом першого модульного регістра пам’яті, третя додатково ведена вхідна шина з’єднана з другим входом другого модульного регістра пам’яті, виходи другого модульного регістра пам’яті з’єднані з відповідними першими входами відповідних додатково введених різницево-модульних матриць, другі входи яких додатково з’єднані з відповідними виходами першого модульного регістра пам’яті, а виходи різницевих матриць додатково з’єднанні з входами відповідних логічних модулів рандомізації.

Патент на корисну модель

ГРИГА ВОЛОДИМИР МИХАЙЛОВИЧ; НИКОЛАЙЧУК ЯРОСЛАВ МИКОЛАЙОВИЧ

Пристрій сортування двійкових чисел, який містить першу вхідну n-розрядну шину, виходи якої з’єднані з відповідними входами першої n-розрядної структури сортування двійкових чисел, другу вхідну n-розрядну шину, виходи якої з’єднані з відповідними входами другої n-розрядноїструктури сортування двійкових чисел, третю 2n-розрядну вихідну шину, яка є виходом пристрою, який відрізняється тим, що виходи першої n-розрядної структури сортування двійкових чисел додатково з’єднані з відповідними першими входами третьої n-розрядноїструктури сортування двійкових чисел, другі входи якої додатково з’єднані з відповідними виходами другої n-розрядної структури сортування двійкових чисел, перші входи першої і другої структур сортування двійкових чисел з’єднані з інверсними кодами відповідних перших чисел, кожен базовий елемент структури пристрою додатково містить два мультиплексори з парафазними виходами, схема порівняння базового елемента сортування містить суматор з прискореним переносом з парафазними виходами а 2N-виходів третьої структури сортування двійкових чисел з’єднані з вихідною шиною.

Патент на корисну модель

ДАВЛЕТОВА АЛІНА ЯРОСЛАВІВНА; ГРИГА ВОЛОДИМИР МИХАЙЛОВИЧ; НИКОЛАЙЧУК ЯРОСЛАВ МИКОЛАЙОВИЧ

Матричний перемножувач належить до засобів обчислювальної техніки і може бут використаний у якості компонента високопродуктивних проблемно-орієнтованих багаторозрядних процесорів опрацювання та шифрування інформації.

Позитивний ефект досягається шляхом додаткового введення вхідного та вихідного синхронізованих регістрів пам’яті. Досягнуто розширення функціональних можливостей та застосування у швидкодіючих цифрових пристроях, цифрових фільтрах та спец процесорах шифрування даних. Додаткове введення у матричний суматор повних однорозрядних двійкових суматорів з парафазними входами та виходами дозволило підвищити швидкість таких перемножувачів у порівнянні з відомими у

разів.

Презентація – чудовий спосіб представити свої ідеї.

Студенти спеціальності «Автоматизація та комп’ютерно-інтегровані технології» чудово втілити свої.